|

Schaltungen digital Master-Slave-Flip-Flop |

|

|---|

|

Schaltungen digital Master-Slave-Flip-Flop |

|

|---|

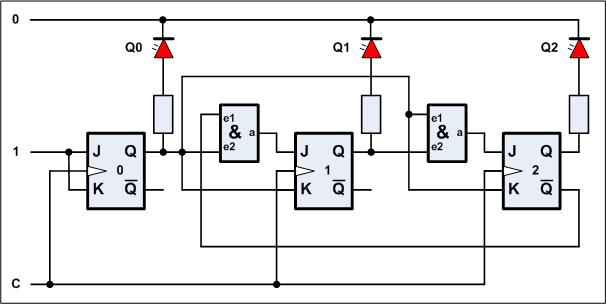

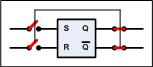

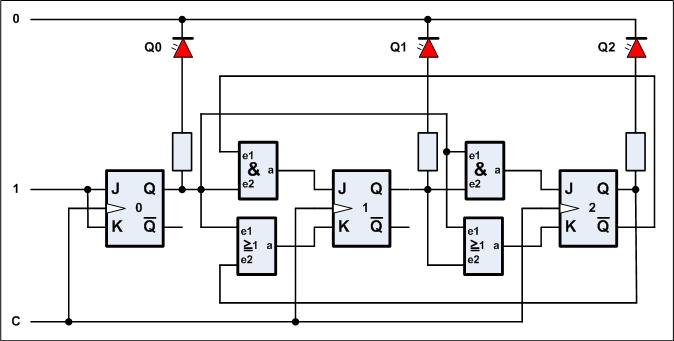

In dem Teil Zähler, Teiler, Register wurden zur Realisierung dieser Schaltungen Flip-Flop's genutzt, z.B. ein Zähler von 0 bis 5:

Die Schaltungen sind vom Prinzip her richtig, nur werden sie so nicht funktionieren.

Das Problem ist, dass die Änderung des Zustandes der Flip-Flops auch gleich am Ausgang

dieser zu sehen ist und sofort zur Berechnung der logischen Eingangswerte genutzt werden

- damit ist es sehr unwahrscheinlich, dass das Ergebnis richtig ist!

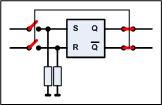

Um das zu verhindern, trennt man bei der der Eingabe zur Einstellung des neuen

Zustandes die Ausgänge einfach ab.

Um das zu verhindern, trennt man bei der der Eingabe zur Einstellung des neuen

Zustandes die Ausgänge einfach ab.  Man muss in dieser Situation den Eingang wegschalten.

Man muss in dieser Situation den Eingang wegschalten.  Mit Pull-Down-Widerständen legen wir 0 auf die Eingänge und erzeugen so exakt den

Speicherzustand - nun sollte es gehen!?

Mit Pull-Down-Widerständen legen wir 0 auf die Eingänge und erzeugen so exakt den

Speicherzustand - nun sollte es gehen!? Und da haben wir ein neues Problem, die am Ausgang nachfolgende Schaltung bekommt

nun einen undefinierten Wert!

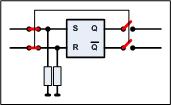

Und da haben wir ein neues Problem, die am Ausgang nachfolgende Schaltung bekommt

nun einen undefinierten Wert! Die Lösung kann also nur sein, am Ausgang einen Speicher anzufügen, der den

eingestellten Zustand auch bei nicht vorhandenem Signal rettet.

Die Lösung kann also nur sein, am Ausgang einen Speicher anzufügen, der den

eingestellten Zustand auch bei nicht vorhandenem Signal rettet.

Das bedeutet also,

will man oben genanntes Problem beseitigen, braucht man in dem

Bauelement immer zwei Flip-Flop's / Latch.

Und man sieht auch sofort, dass sie nicht zur gleichen "Zeit" zugeschaltet werden

können, das Ergebnis steht nun immer etwas später zur Verfügung - das wollten wir so!

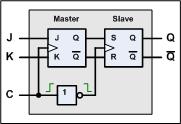

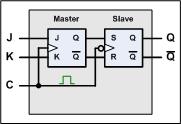

Diese Anordnung aus zwei Latch/Flip-Flop's wird als Master-Slave-Flip-Flop

bezeichnet, wobei das erste Flip-Flop als Master bezeichnet wird und für die

Einstellung und Speicherung der Zustände verantwortlich ist.

Der Slave, das zweite Flip-Flop speichert und gibt die Zustände des Masters

verzögert aus.

Nun sollte unsere Schaltung funktionieren!

Als nächstes ist damit zu klären, wo man die beiden Signale herbekommt?

Da der Nutzer nun nicht auch noch zwei Signale zur Steuerung erzeugen muss, leitet

man die Signale aus dem Takt ab. Das kann beim Takt zum Einen der High- oder Low-Pegel

und zum anderen der Übergang von low zu high, wir sagen ansteigende Flanke, oder

von high zu low, abfallende Flanke sein.

Man spricht nun von zwei Zustands gesteuerten Latch (Flip-Flop's)

oder von zwei Flanken gesteuerten Flip-Flop's.

Bei MERTECH wird eine Liste aller

möglichen Kippglieder vorgestellt!

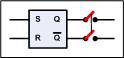

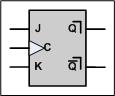

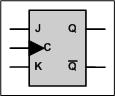

Aus der Symbolik sollte man sofort erkennen, um welches Kippglied es sich handelt:

Es ist ein JK-Master-Slave-Flip-Flop, was mit ansteigender Flanke den Zustand ändert

und mit abfallender diesen am Ausgang bereitstellt.

Es ist ein JK-Master-Slave-Flip-Flop, was mit ansteigender Flanke den Zustand ändert

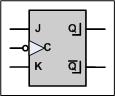

und mit abfallender diesen am Ausgang bereitstellt. Es ist ebenfalls ein JK-Master-Slave-Flip-Flop, ändert jedoch mit abfallender Flanke

den Zustand und gibt ihn bei ansteigender aus.

Es ist ebenfalls ein JK-Master-Slave-Flip-Flop, ändert jedoch mit abfallender Flanke

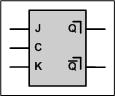

den Zustand und gibt ihn bei ansteigender aus.  Dies beschreibt ein Zustand gesteuertes JK-Master-Slave-Flip-Flop, welches bei

high-Pegel den Zustand aktualisiert und bei low-Pegel diesen ausgibt.

Dies beschreibt ein Zustand gesteuertes JK-Master-Slave-Flip-Flop, welches bei

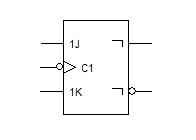

high-Pegel den Zustand aktualisiert und bei low-Pegel diesen ausgibt. In WikiBooks findet man dieses Symbol -

In WikiBooks findet man dieses Symbol -  Dafür kann man dann das einfachere "mit einer abfallende Flanken" gesteuerte

JK-Flip-Flop nutzen.

Dafür kann man dann das einfachere "mit einer abfallende Flanken" gesteuerte

JK-Flip-Flop nutzen.

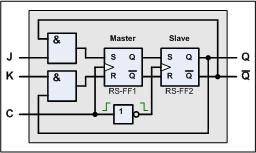

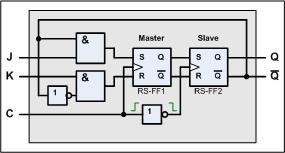

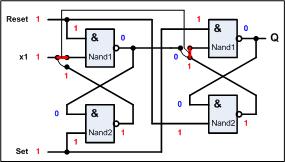

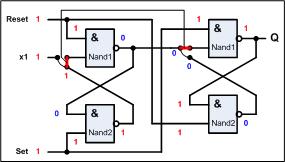

Als nächstes wollen wir uns die Realisierung eines Master-Slave-Flip-Flop's ansehen.

Gebraucht wird meist ein JK-Master-Slave-Flip-Flop. Als Forderung an diesen Baustein

stehen:

oder

oder

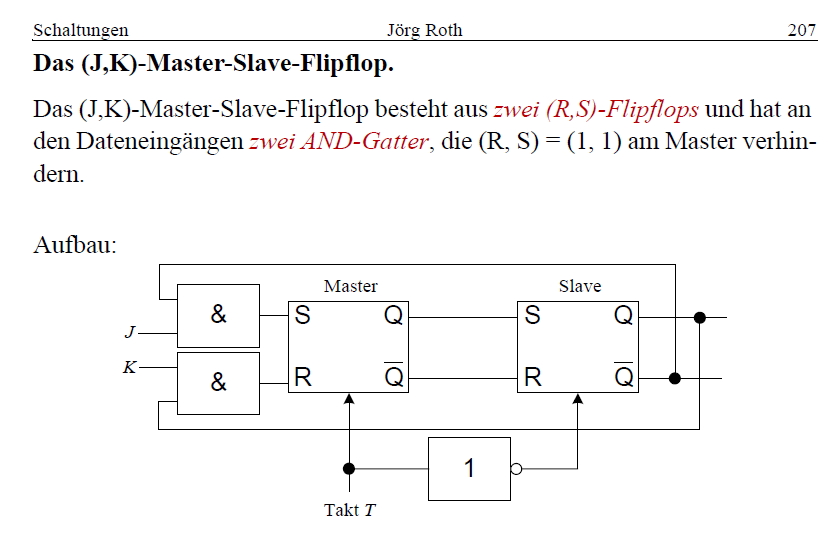

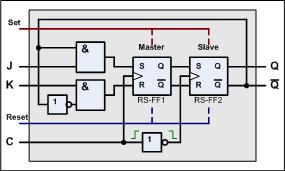

Nun bedarf es zwar 2 weiterer AND-Gatter, die wurden aber auch am Eingang des Masters gebraucht, aber Master und Slave sind nun nur noch RS-Flip-Flop's. Weiterhin kann diese Anordnung, da es auch noch die Forderung nach SET und RESET gibt, von Vorteil bei der technischen Realisierung sein.

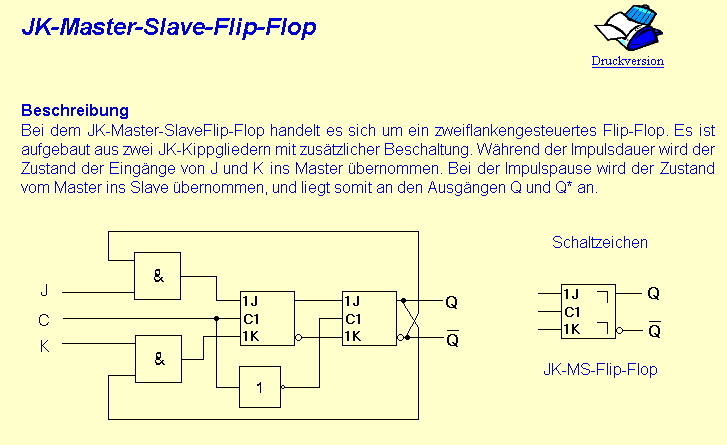

Recherchiert man im Internet nach Master-Slave-Flip-Flop's, erhält man die unterschiedlichsten Beschreibungen. Bei "Bibian" findet man Folgendes:

Wie bereits dargestellt, sind als Master und Slave keine JK-Flip-Flop's erforderlich, es wird sicher so funktionieren. Das Problem ist die Darstellung, die Kipglieder sind nach Definition "ein Zustand gesteuerte JK-Latch", die gibt es nicht. Unklar ist auch, was bei einer Flankensteuerung eine Impulspause ist?

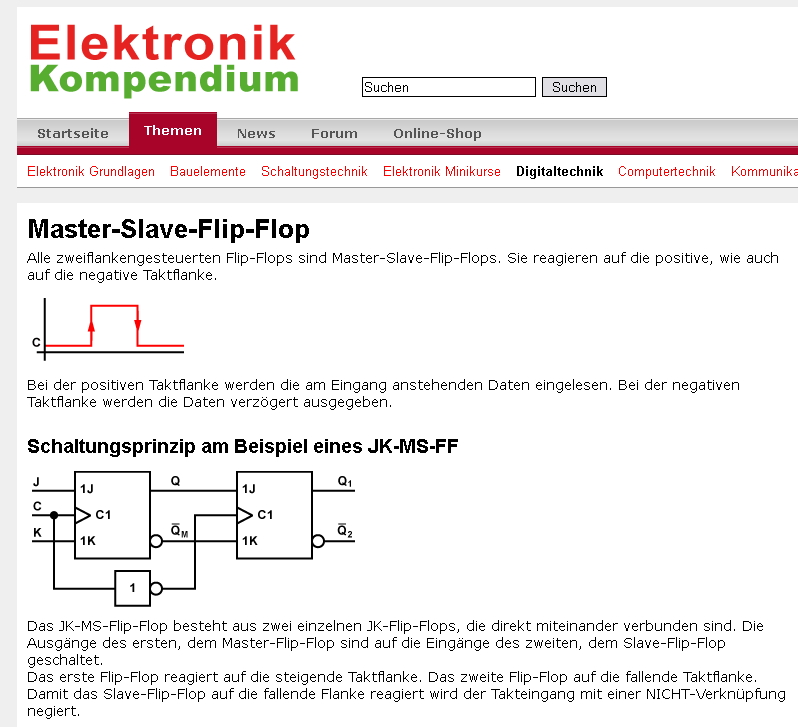

Beim "Kompendium Elektronik" wird ebenfalls eine Variante dargestellt und beschrieben, das entspricht weitgehend der oben gemachten Darstellung, lediglich wird auch der Slave wieder unnötiger Weise durch ein JK-Flip-Flop realisiert:

Die Beschreibung der "FH-Nürnberg" entspricht weitgehend den bisherigen Darstellungen.

Allerdings ist die Zuführung des Taktsignals zu den RS-Latch nicht eindeutig,

entspricht nicht der vereinbarten Symbolik!

Lösungen der Industrie

Von Interesse sollte an dieser Stelle sein, was denn die Industrie als

Master-Slave-Flip-Flop's anbietet.

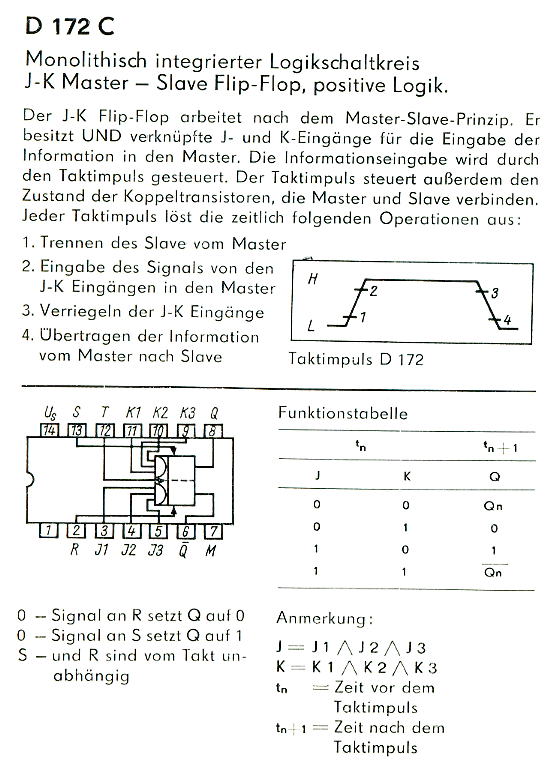

Vor 1974 standen die Schaltkreise SN7472 und D172 zur Verfügung beide sind annähernd

gleich, haben die gleiche Funktion.

Aus einem alten RFT Bauelemente-Katalog von

1974/75 habe ich folgende Daten entnommen:

|

Sehr gut ist, dass hier noch einmal die Funktionsweise beschrieben wird. Dieses Master-Slave-Flip-Flop verfügt ebenfalls über einen SET- und RESET-Eingang. Für J und K gibt es jeweils 3 AND verknüpfte Eingänge.

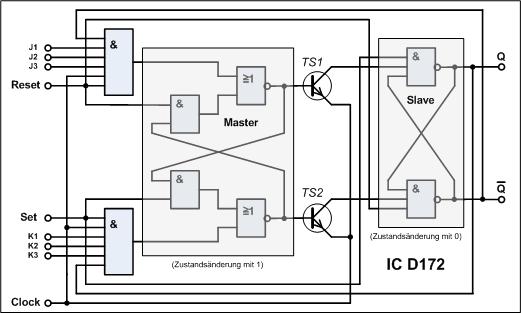

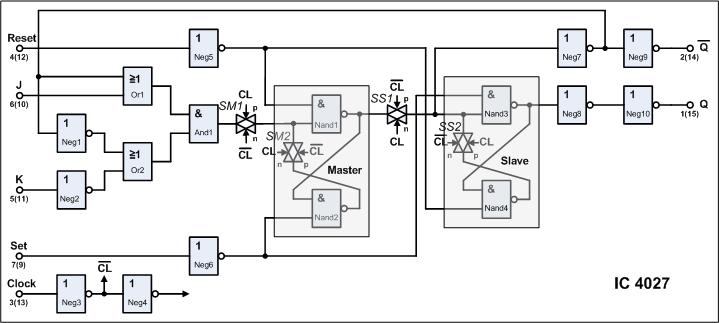

In einem Blockschaltbild kann man den logischen Aufbau des Flip-Flop's sehen.

Die Darstellung des Blockschaltbildes ist etwas ungewöhnlich, sie entspricht nicht unseren Vorstellungen bezüglich Master und Slave. |

Das Blockschaltbild wurde deshalb in eine vergleichbare Form umgezeichnet.

|

Sehr deutlich wird nun das Prinzip sichtbar. Es wird das JK-Prinzip über Master und Slave gezogen (gekreuzte Ausgänge an den Eingang gelegt), Master und Slave sind RS-Latch. Die Art, wie nun die einzelnen Teile realisiert werden, hängt von den Möglichkeitet der Realisierung der logischen Bauelemente auf dem Kristall ab. Und natürlich spielt auch die Cleverness des Designers eine entscheidende Rolle bei der Realisierung. Der Master wird mittels NOR-Bausteinen erzeugt. Das AND-Gatter in der Rückführung kann mittels Set- oder Reset-Signals das Rückführen einer 1 verhindern. Die Zustandsänderung erfolgt mit 1, jedoch sind die Ausgänge Q und Qn vertauscht. Das hat aber den Vorteil, dass sie so sofort als Eingang für den Slave genutzt werden können, denn ist Q=1, dann ist Qn=0 und da der Slave mit NAND's realisiert wird, verändert der mit 0 den Zustand, das ist dann wieder richtig. Ist der Takt 0, dann sind die Eingänge am Master gesperrt, denn "0 AND x = 0", das Gatter kann nur eine 1 ausgeben, wenn mindest der Takt auch 1 ist. Am Transister, der die oben beschriebene Schaltfunktion übernimmt, liegt am Emitter 0, mit 1 an der Basis kann der Transistor diese zum Slave durchstellen. Ist der Takt 1, wird der Eingang am Master frei gegeben, denn "1 AND x = x". Beim Transistor wird der Emitter auch auf 1 gelegt, der kann nun nicht mehr schalten, er hat einen großen Widerstand zwischen Basis und Kollektor. |

Es handelt sich bei diesem Flip-Flop um einen Zustand gesteuertes Kippglied und ist

eigentlich ein Latch,

es handelt sich um ein "zwei Zustands gesteuertes JK-Master-Slave Latch".

(IC D172; nach RFT Bauelemente-Katalog; 1974/75) |

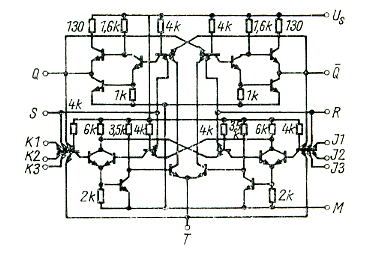

Ganz kurz wollen wir noch einen Blick auf die verwendete Technologie werfen. Zu der Zeit (vor 1975) wurde die TTL-Technologie verwendet. Alle logischen Bauelemente wurden aus bipolaren Transistoren und Widerständen erstellt. MOSFET's gab es schon, aber die CMOS-Technologie war erst in den Anfängen, es gab noch keine Schaltkreise auf dieser Basis. So sah dann die Realisierung des D172 aus, der wesentlicher Fortschritt war der Mehr-Emitter-Transistor. Weitere Informationen findet man im Teil: " NAND/NOR DTL - TTL - MOSFET - CMOS". |

|

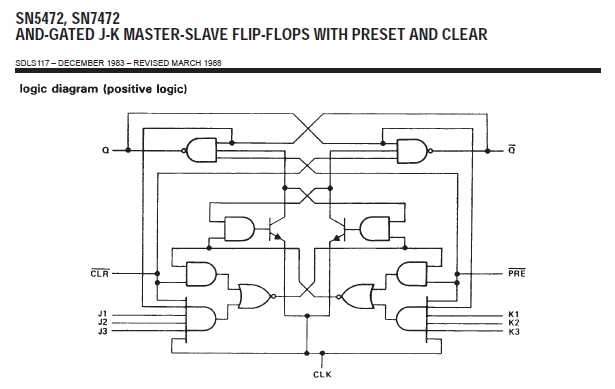

Das ist das Blockschaltbild vom SN7472 (nach Datenblatt TEXAS INSTRUMENTS 1988). Das Konzept ist mit dem D172 identisch, lediglich die Kopplung zwischen Master und Slave wird komplexer gelöst. (PRESET entspricht dem SET, CLEAR dem RESET) |

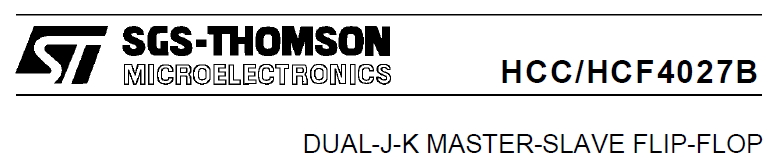

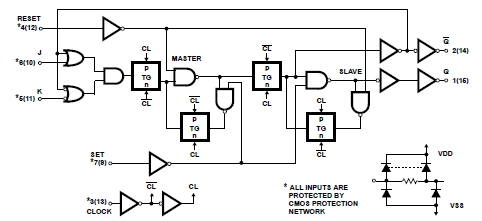

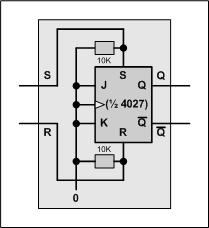

Ein aus der neueren Zeit ist der JK-Master-Slave-Flip-Flop 4027, er wurde mit den Möglichkeiten der CMOS-Technologie erstellt.

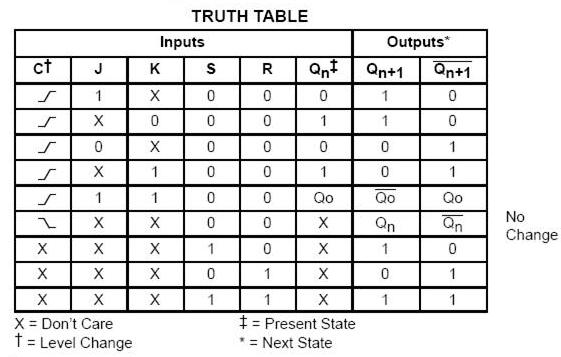

Das Flip-Flop interessierte mich auch deshalb, weil die Zustandsübergangstabelle es zuläßt, das Master-Slave-Flip-Flop auch als ein ganz einfaches RS-Latch zu nutzen:

Ist S oder R gleich 1, können C, J und K beliebige Werte annehmen (Don't Care), sie haben keinen Einfluss auf das Setzen (3 letzten Zeilen der Tabelle). Da die Eingänge nicht offen bleiben können, setze ich J, K und C einfach auf 0.

|

Die neue Technologie und natürlich die gewachsene Erfahrung beim Designen eines

Schaltkreises schaffen neue Lösungsansätze. Bisher wurden die gekreuzten Ausgänge verwendet - das muss nicht sein, man braucht nur ein Signal wieder nach vorne führen und erzeugt das andere mit einem Negator. Denn es kann durchaus sein, dass eine Leitung mehr Probleme auf dem Chip bereitet als ein Negator. Zu überlegen ist auch, ob die Eingangslogik auf nur ein Signal zu beschränken ist. |

|

Eine weitere Option im gesamten Konzept ist das Einbringen von SET und RESET. Diese Möglichkeit ist sehr notwendig bei der Anwendung des Schaltkreises, z.B. bei Zählern das Setzen eines bestimmten Anfangswertes. |

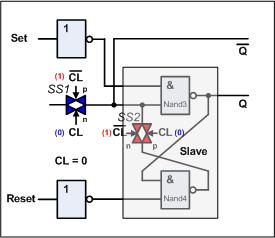

So sieht zu diesem Flip-Flop das Logik-Blockschaltbild aus:

Die Darstellung mit den bisher verwendeten Symbolen soll die Basis der weiteren Beschreibung sein. Master und Slave wurden in der üblichen Weise dargestellt.

|

Ein paar grundlegende Konzepte erkennt man sofort:

Die Symbole sind alle bekannt, bis auf:  Es wird damit ein Transmissions Gate (deshalb in der Schaltung oben TG) dargestell. Dieses Teil hat eine wichtige Funktion, denn würde es fehlen, würden die Ausgäng von "NAND2" und "AND1" parallel geschaltet, das kann zerstörende Wirkung haben, TG's müssen wie Schalter funktionieren! |

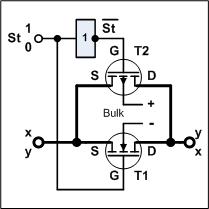

Ein Transmission-Gate hat etwa folgende Schaltung:

|

Das parallel schalten eines nMOS und pMOS bewirkt, dass die Verbindung xy etwa wie ein Relais-Kontakt funktioniert. Es ist egal auf welcher Seite sich die Quelle befindet. Wird der pMOS (oben) mit 1 und der nMOS (unten) mit 0 angesteuert, wird die Strecke xy sehr hochohmig, Schalter offen. Bei Ansteuerung mit 0 und 1 hingegen geht der Widerstand der Strecke xy gegen Null, Schalter geschlossen. |

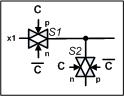

Man kann in der Schaltung des Flip-Flop's folgende Anordnung 2 mal finden:

Die beiden TG's werden entgegengesetzt angesteuert. ist C=0, dann wissen wir aus

der Beschreibung eben, dass das waagerechte (S1) TG leitend (geschlossener Schalter),

das senkrechte (S2) hingegen sperrend (offener Schalter) ist. Man hat somit einen

Umschalter:

Die TG's vor dem Slave sind zu dem am Master genau entgegengesetzt geschaltet.

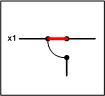

Somit kann man nun eine symbolische neue Darstellung finden:

Das ist völlig richtig, denn wird der Zustand beim Master geändert, ist der Slave

weggeschaltet, er speichert die alten Werte. Übernimmt der Slave die Daten vom

Master, ist der Master im Speicherzustand, er übernimmt keine Werte vom Eingang.

Aber,

man muss schon genau hinsehen, um festzustellen, dass der Designer hier mächtig

getrickst hat, denn bei der Übernahme der Werte in Master oder Slave

gibt es diese gar nicht, es gibt kein Latch!

Die Rückkopplung vom Ausgang des unteren Gatters auf den Eingang des

oberen Gatters gibt es nicht, die beiden NAND's wirken nun einfach wie zwei Negatoren

(sofern das SET und RESET-Signal 1 ist - ist es, da beide vor dem Negator auf 0 liegen)

in einer Folgeschaltung. Die beiden Gatter haben somit ein genau entgegengesetzten

Wert. Schaltet der Schalter sehr schnell um, haben wir ein RS-Latch mit genau den

eingestellten Werten auf den beiden NAND's, die aber nun gespeichert werden.

Man kann so den "Zustand" der "Latch" mit 1 oder 0 ändern, das finde ich genial.

So ist es dann auch verständlich, dass nur ein Signal zur "Zustandsänderung" gebraucht

wird, weil es gar keine Zustandsänderung ist!

Das funktioniert nur deshalb, weil die CMOS-Realisierung beim Gate immer eine

Kapazität erzeugt, die in diesem Fall speziell für diesen Effekt etwas vergrößert

sein könnte.

Die Werte werden damit kurzzeitig (Umschaltzeit) kapazitiv gespeichert.

Im Folgenden soll noch einmal die gesamte Realisierung des Schaltkreises mit

CMOS-Baugruppen gezeigt werden. diese wurden aus dem Teil:

" NAND/NOR DTL - TTL - MOSFET - CMOS"

übernommen und abgeleitet.

Die Realisierung bedarf dann doch so etwa 31 CMOS Elemente, das wird etwas unübersichtlich.

Es gibt nach der Bauelementeliste der 4000-er Reihe noch 2 weitere JK-MS-FF. Das ist der Baustein 4095 bzw 4096. Die Realisierung des Master-Slave-Prinzip ist mit dem 4027 identisch, verändert werden die J und K Eingänge. Hier gibt es wie beim D172 bzw. SN7472 jeweils drei durch AND gekoppelte Eingänge, teilweise werden sie aber auch noch negiert.

Nun aber noch einmal zurück zur Frage, wieso das JK-Master-Slave-Flip-Flop 4027 als RS-Latch betrieben werden kann?

Das linke Bild zeigt, wie das Bauelement außen beschaltet wurde. J, K und C werden

auf 0 gelegt. Die Widerstände sind Pull-Down-Widerstände und müssen nur sein, wenn

R und S mit einem Schalter auf 1 gesetzt werden, sonst ist der Eingang offen.

Interessant ist für diesen Fall der Slave, denn nur der gibt die Werte aus.

Das rechte Bild zeigt die Situation. Der Schalter (Transmission-Gate) SS1 wird mit

dem Taktpegel CL=0 geöffnet, denn mit CL=0 ist der nMOS gesperrt und mit dem

negierten Signal von CL (Wert=1) der pMOS ebenfalls gesperrt, dh. es gibt keine

Verbindung zum Master, ist also egal was er macht!

Schalter SS2 hingegen, ist mit dieser Einstellung geschlossen, damit haben wir

die Schaltung eines RS-Latch. R und S werden mittels Negator negiert und nehmen

somit exakt passend zu den Vorschriften mit dem Wert 1 eine Änderung des

Zustands vor (siehe dazu auch Teil:

"RS-Flip-Flop").

Am Beispiel des JK-Master-Slave-Flip-Flop wurde das Prinzip Master-Slave beschrieben.

Solche Kippglieder gibt es auch für RS und D Flip-Flop's.

Das JK-MS-FF ist jedoch das meist benutzte, es ist sehr günstig einsetzbar.

Das lieg daran, dass man z.B. aus dem Zustand Q=1/Qn=0 in den entgegengesetzten

immer mit 2 Möglichkeiten kommt, mit J=0/K=1 (reset) oder J=1/K=1 (kippen). Die

technische Realisierung einer Anwendung wird in der Regel dadurch einfacher als

mit den anderen MS-FF.

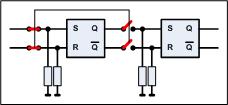

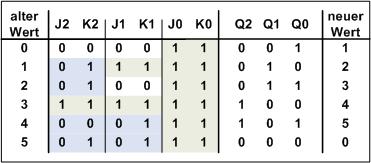

Als Beispiel soll für die folgende Schaltung eine Tabelle für die Belegung von J und K gezeigt werden:

|

Mit der Schaltung wird ein synchroner Zähler von 0 bis 5 realisiert. Die Schaltung kann weiter vereinfacht werden, das spielt aber hier keine Rolle. J0 und K0 werden ständig auf 1 gesetzt, der Ausgang Q0 "kippt" ständig zwischen 1 und 0. Anders hingegen der Zustand von FF2, obwohl Q2 dreimal hintereinander 0 ist, wird das einmal mit "speichern" und zweimal mit "reset" erreicht. "set" wird überhaupt nicht genutzt, soll Q auf 1 gesetzt werden, nutzt die Schaltung "kippen". |

|

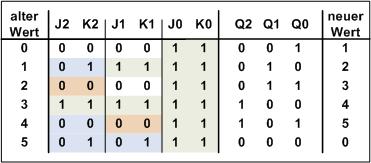

Nutzt man die am Anfang gezeigte

Schaltung

für die Lösung der gleichen Aufgabe

(Zähler von 0 bis 5 - das wäre z.B. die 2.Stelle der Sekunden und Minuten einer

Digitaluhr),

ist die Tabelle an den zwei gekennzeichneten Stellen geändert. |

JK-MS-FF lassen eben vielfältige Lösungen zu!

|

|

zurück zur Start-Seite |