|

Technischer Aufbau des Prozessors 8086 |

|

Technischer Aufbau des Prozessors 8086 |

|

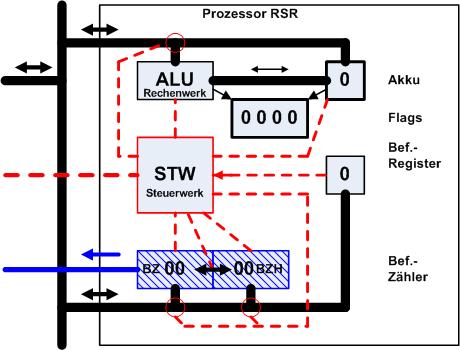

Wir hatten ein Arbeitsregister, den Akku, zur Verfügung.

Von hier aus konnten Daten zum Speicher transportiert werden und zurück. Die ALU

nutzt das Register als Ergebnisspeicher und zur Speicherung eines Operanden. In das Befehlsregister werden alle Werte gespeichert, die als Befehl interpretiert werden sollen. Der Befehlszähler (Register) speichert und bearbeitet die Arbeitsspeicher-Adressen (Befehls- und Datenadressen). Ein Flag-Register mit nur zwei auswertbaren Flags war ebenfalls vorhanden. Das Steuerwerk steuert auf Basis des Wertes aus dem Befehlsregister den gesamten Ablauf im Rechner - eigentlich schon ganz schön viel, was das kleine System können muss. Und wir konnten damit auch ordentliche Programme bearbeiten. |

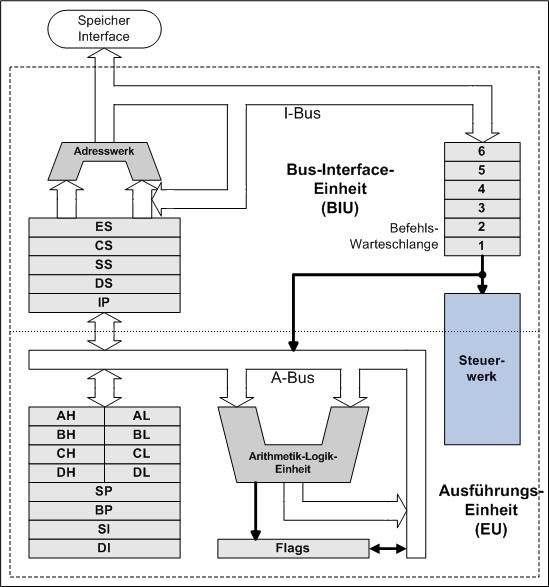

Der 8086 ist ein wesentlich komplexeres Gebilde, so dass nur noch eine prinzipielle Darstellung möglich ist, aber die, die der Programmierer nutzen kann.

|

Als wesentlich neu fällt auf, dass es zwei große Teile im Prozessor gibt:

Die Trennung in die zwei Bereiche ist sehr nützlich, denn, dadurch das die EU

mit einer Reihe weiterer Register ausgestattet ist, kann die ALU völlig autonom

nur mit den Registern rechnen.

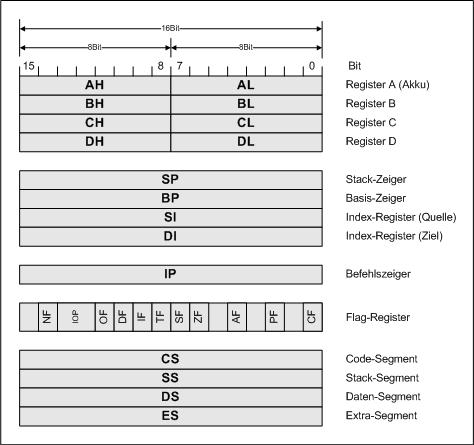

In der EU sind die Register A bis D die Arbeitsregister. Man kann sie z.B. mit AX als

16Bit Register ansprechen oder auch mit AH (oberer Teil) oder AL (unterer Teil)

jeweils als 8Bit Register nutzen. Für den Nutzer ist eigentlich nur wichtig, welche Register genutzt werden können und er muss wissen, ob sie genutzt werden können oder dort wichtige Werte stehen! |

Deshalb reicht für die Bearbeitung von Programmen nur der Register-Plan:

|

Die Register werden mit der deutschen Bezeichnung beschrieben. Zusätzlich gibt es auch eine Bezeichnung der Flags im Flagregister. Man findet wieder die 4 aus dem Prozessor ERNA bekannten Flags: ZF (Zero-Flag (Null)), SF (Sign-Flag (Vorzeichen)), CF (Carry-Flag (Übertrag)) und das OF (Overflow-Flag (Überlauf)). Auf Grund der 16 Bit sind nun noch 12 weitere Flags möglich, es sind jedoch nur insgesamt 11. Mehr Register sind natürlich toll, aber man braucht auch mehr Befehle um das alles bedienen zu können. Nehmen wir nur einmal die 4 Datenregister A bis D:

Dafür sind dann bereits 44 Befehle notwendig. Aber wir haben bisher nur Transportbefehle gezählt, es gibt ja auch noch arithmetische, logische und Flag Auswerte-Befehle und weitere - man sieht, wir brauchen eine größere Verarbeitungsbreite. Mit 16Bit besteht aber die Möglichkeit 65536 verschiedene Befehle zu identifizieren, das reicht, das wird nicht im 8086 genutzt. |

Damit können wir uns dem nächsten Thema widmen, der

Adressierung von Speicherplätzen

|

|

zurück zur Start-Seite / weiter Adressierung von Speicherplätzen |

|